News - Baugruppen- und System-Test

Integrierte Plattform für Soft- und Hardware-Validierung und Test

Integrierte Plattform für Soft- und Hardware-Validierung und Test

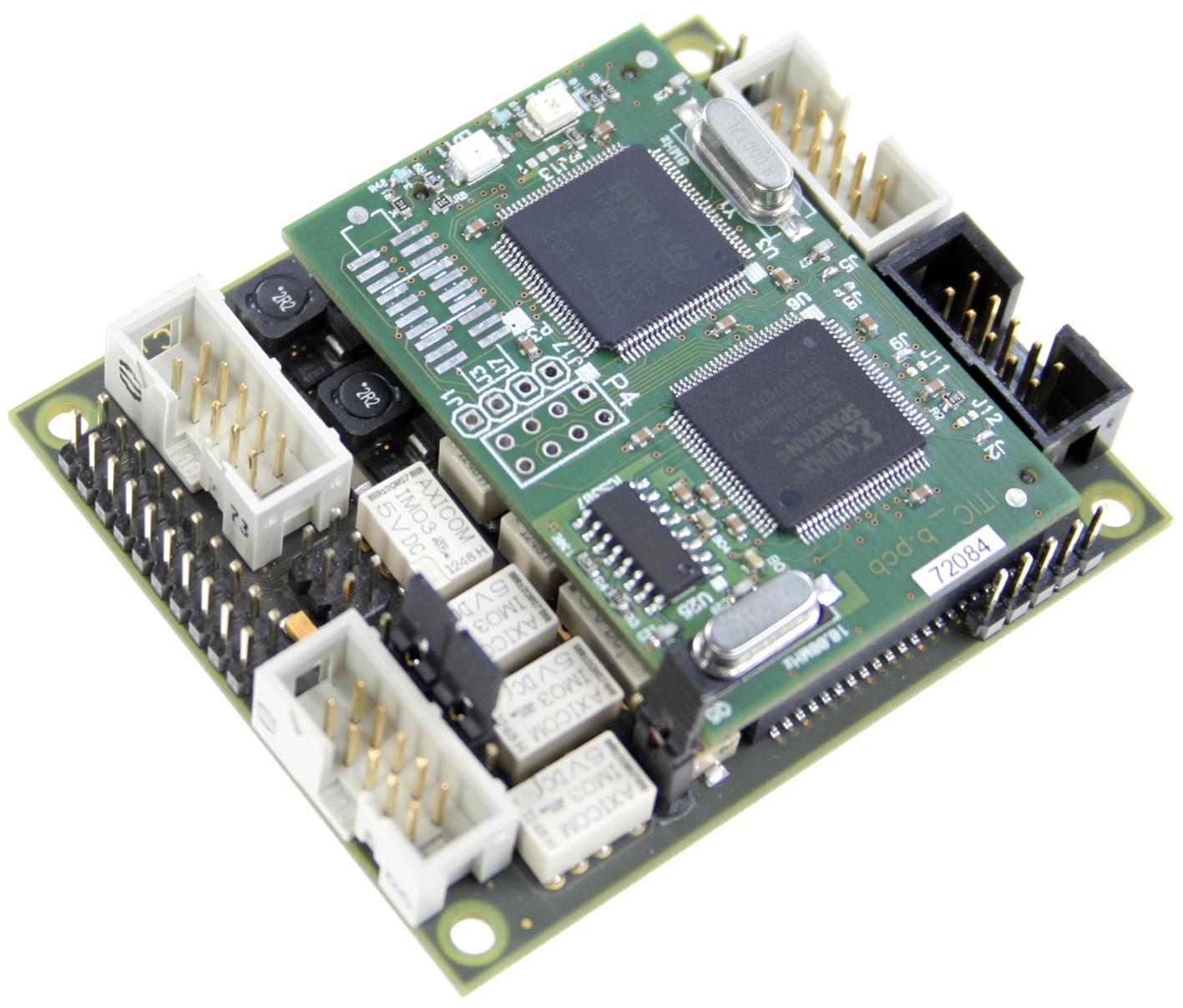

20. September 2013 - GÖPEL electronic und iSYSTEM haben unter der Bezeichnung iTIC eine Plattform für die Soft- und Hardware-Validierung und den Test entwickelt, die erstmals einen kompletten On-Chip Debugger als TAP Interface Card (TIC) nahtlos in die ESA-Hardwareplattform SCANFLEX von GÖPEL integriert.

Angesteuert über das interne Standardinterface der TAP Interface Cards unterstützt das iTIC sowohl Prozeduren zum Software-Debugging, als auch alle weiteren Technologien zum Embedded System Access (ESA) wie Boundary Scan, Prozessor Emulation Test, FPGA Assisted Test und In-System Programmierung von Flash und PLD.

„Das neue iTIC ist ein ganz wichtiger Meilenstein in der ganzheitlichen Umsetzung unserer Philosophie des Embedded System Access. Durch die erfolgreiche Kooperation mit unserem langjährigen Partner iSYSTEM sind wir jetzt nicht nur in der Lage, eine noch größere Anzahl von Mikroprozessoren zu unterstützen, sondern können noch gezielter Synergien zwischen den verschiedenen Anwendungen erschließen“, freut sich Thomas Wenzel, Geschäftsführer der JTAG/Boundary Scan Division bei GÖPEL electronic. „Die Möglichkeit, alle diese Prozeduren auf einer Plattform auszuführen, bedeutet für die Anwender ein Gewinn an Effektivität bei der Design-Validierung und Flexibilität beim Test über den gesamten Produktlebenszyklus.“

„Wir haben in den letzten Jahren die Connectivity unserer Tools zur Entwicklung und zum Test von embedded Software und die dazugehörigen Partnerschaften mit Anbietern komplementärer Produkte systematisch ausgebaut, um für unsere Kunden einen deutlichen Mehrwert an Einsatzeffizienz und Leistungsfähigkeit zu schaffen“, erläutert Erol Simsek, Geschäftsführer bei iSYSTEM AG. „Gestützt auf die intensive Zusammenarbeit mit GÖPEL electronic als Marktführer bei Embedded System Access Technologien setzen wir diesen Kurs weiter fort und erweitern darüber hinaus auch unsere Aktivitäten als OEM-Lieferant.“

Das iTIC ist bereits das siebente Mitglied in der Familie von TAP Interface Cards (TIC) und wird genau wie die anderen über eine differentielle Schnittstelle angesteuert. Daher können vorhandene Installationen einfach aufgerüstet werden.

Durch die differentielle Kopplung sind störsichere Datenübertragungen bis 80 MHz über Entfernungen bis 4 m problemlos realisierbar. Ein Performanceverlust entsteht dadurch nicht, da die Laufzeitverzögerungen der Kabel und der Unit Under Test (UUT) durch die ADYCS™ Technik pro TAP individuell kompensiert werden können. Daher kann das iTIC auch in applikationskritischen Umgebungen wie In-Circuit Test Fixtures integriert werden.

Konzipiert als aktiver Testkopf unterstützt das iTIC eine Fülle von verschiedensten Operationen und Prozessorarchitekturen. Dazu gehören Standards wie IEEE1149.1, IEEE1149.6, IEEE1149.7, IEEE1532 und IEEE-ISTO 5001, sowie eine Fülle von non JTAG Interfaces wie BDM (Background Debug Mode), SBW (Spy-Bi-Wire), SWD (Serial Wire Debug) und viele weitere. Dabei kann das Target Interface über Relais komplett galvanisch abgetrennt werden.

Softwareseitig wird das iTIC von der führenden JTAG/Boundary Scan Software SYSTEM CASCON™ unterstützt und durch das AutoDetect Feature automatisch erkannt. Durch die OEM-Kooperation mit allen führenden Anbietern von In-Circuit-Testern (ICT), Manufacturing Defect Analyzers (MDA), Flying Probern (FPT) und Funktionstestern (FCT) steht die neue Lösung auch sofort für die Produktion zur Verfügung.

Über Embedded System Access (ESA):

ESA Technologien ermöglichen den elektrischen Zugriff auf Embedded Systeme ohne den Einsatz von mechanischen Nadelkontakten oder Proben (nichtinvasive Verfahren). Dazu nutzen sie designintegrierte Test- und Debugschnittstellen wie beispielsweise JTAG. Zu den ESA-Technologien gehören neben Boundary Scan, auch Verfahren wie Chip Embedded Instruments, Processor Emulation Test, FPGA Assisted Test, FPGA Assisted Programming, In-System Programming oder Core Assisted Programming. ESA-Technologien sind die derzeit modernsten Strategien zur Validierung, Test, Debugging, sowie zur Programmierung komplexer Chips, Boards und kompletter Units, können über den gesamten Produktlebenszyklus eingesetzt werden und ermöglichen verbesserte Testabdeckung bei verringerten Kosten.

www.goepel.com/